April 2025

The global 3D semiconductor packaging market size was valued at US$ 11.00 billion in 2023 and is projected to hit US$ 57.19 billion by 2034, upsurging at a CAGR of 16.17% during the forecast period from 2024 to 2034. With widespread digitalization, 3D semiconductor industry is growing that is directly boosting the demand for 3D semiconductor packaging market.

![]()

Increased trend for miniaturization of electric devices has risen demand for the 3D packaging semiconductor. The key players operating in the market are focused on adopting inorganic growth strategies like acquisition and merger to develop advance technology for manufacturing 3D packaging for semiconductors which is estimated to drive the global 3D semiconductor packaging market over the forecast period. Increasing in adoption of the advanced technology for the production of 3D packaging semiconductor is estimated to drive the growth of the global 3D semiconductor packaging market in the near future.

3D packaging in semiconductors refers to the integration of multiple semiconductor devices into a single package, arranged in a three-dimensional configuration. This approach contrasts with traditional 2D packaging methods, where components are laid out in a flat, two-dimensional manner. 3D packaging allows for stacking multiple chips (die) vertically. This can include several types of chips, such as logic, memory, and sensors, providing a compact solution that reduces the footprint of electronic devices. Several types of technology are used in 3D packaging which have been mentioned here has follows: TSV Technology, Wafer-Level Packaging (WLP), System-in-Package (SiP) and Chip-on-Wafer (CoW) and Wafer-on-Wafer (WoW).

The 3D semiconductor packaging provides various benefits which have been mentioned here as follows: space efficiency, performance improvements, thermal management, power efficiency, and design flexibility. The 3D packaging semiconductor reduces the overall size of electronic devices by stacking components, crucial for applications in mobile and wearable technologies. It even enhances performance due to shorter interconnects, leading to lower latency and higher bandwidth. This is particularly important for high-performance computing and data-intensive applications. 3D semiconductor packaging reduces power consumption by shortening the distances that signals must travel, which is beneficial for battery-operated devices.

3D semiconductor technology represents a significant advancement in the miniaturization and performance of electronic devices. By stacking multiple chips and integrating various functionalities into a compact form factor, it meets the growing demands of modern applications while posing challenges that require innovative solutions in manufacturing, thermal management, and reliability. As technology continues to evolve, 3D packaging is expected to play a crucial role in the future of semiconductor design and manufacturing.

AI can significantly enhance the 3D packaging semiconductor industry in several ways by providing design optimization, automated layout design, process automation, providing thermal management solutions, and providing enhanced testing and validation. AI algorithms can optimize the layout of components within a 3D package, improving space utilization and reducing signal interference. AI can simulate thermal and electrical performance during the design phase, allowing for better predictions of behaviour under different conditions.

AI-driven automation can streamline the manufacturing process, reducing cycle times and minimizing human error. Machine learning algorithms can analyze data from production lines in real-time, identifying defects and ensuring consistent quality. By leveraging AI technologies, the 3D packaging semiconductor industry can achieve greater efficiency, reduced costs, and enhanced performance, ultimately driving innovation and competitiveness in the market.

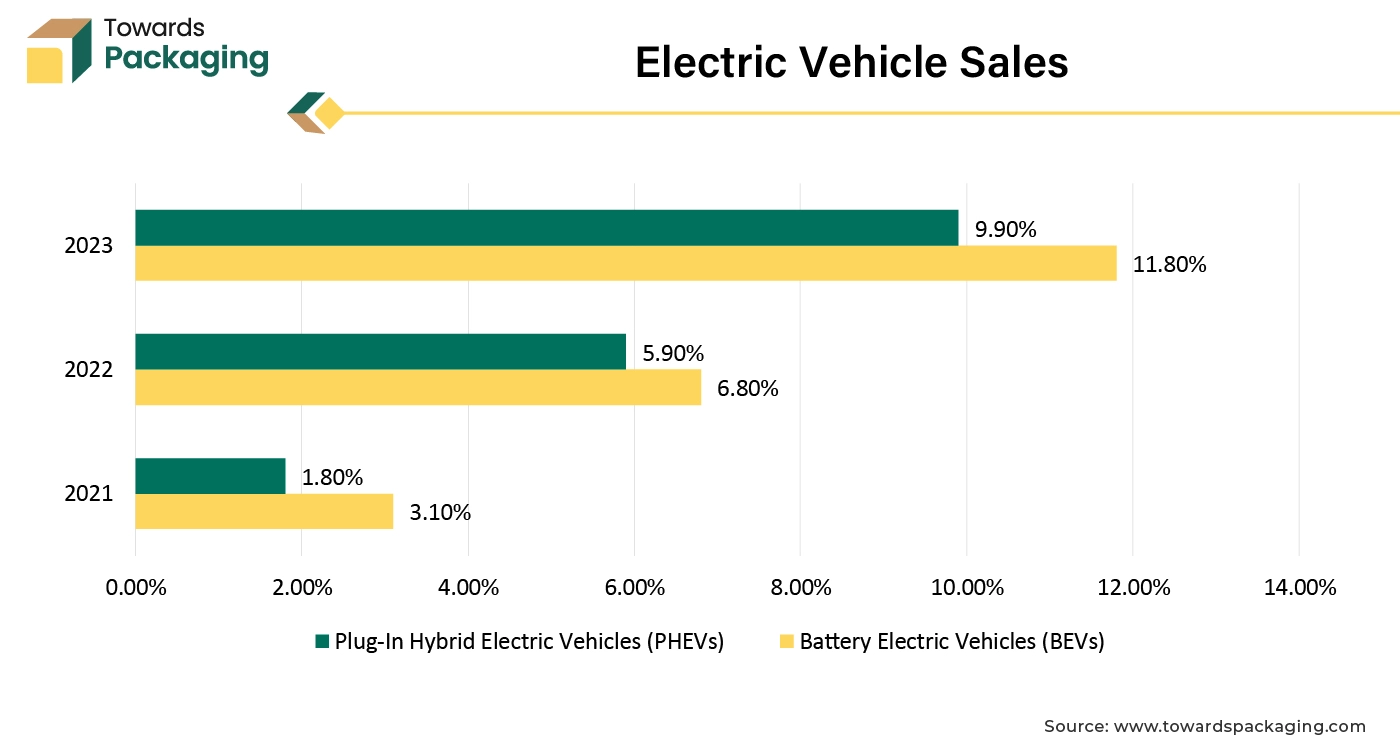

The rise of electric vehicles and advanced driver-assistance systems (ADAS) requires sophisticated electronics that benefit from 3D packaging for space and performance optimization. The increase in the innovation and launch of the electric vehicles is estimated to drive the 3D semiconductor packaging market. As the electric vehicles avoid fuel price hikes, the demand for the electric vehicles is rising at fast rate. 3D packaging reduces the physical footprint of semiconductor components, allowing for more efficient use of space within the vehicle, which is crucial in the compact environments of EVs. EVs require high-performance electronics for efficient power management and conversion. 3D packaging helps achieve lower resistance and improved thermal management, enhancing overall performance. As the EV market grows, manufacturers seek cost-effective solutions.

The key players operating in the market are facing challenges in fulfilling the regulatory norms by the regulatory bodies as well as technical challenges, which is observed to restrict the growth of the 3D semiconductor packaging market. The absence of industry-wide standards for 3D packaging can hinder widespread adoption and create uncertainties in manufacturing and supply chains. Meeting varying regulatory requirements across different regions can complicate the manufacturing and deployment of 3D packages.

The materials used in different chips must be compatible, which can limit design choices and complicate the manufacturing process. Ensuring that materials used can withstand the stresses of 3D packaging, such as thermal expansion and mechanical strain, is critical. Ensuring effective heat dissipation in densely packed structures remains a significant challenge, as overheating can affect performance and reliability. Long-term reliability of interconnections in 3D packages can be uncertain, leading to potential failures that are difficult to diagnose.

The advanced manufacturing processes required for 3D packaging, such as through-silicon vias (TSVs) and wafer-level packaging, can be costly. Significant investment is needed for specialized equipment and technology, which can be a barrier for smaller companies. While the 3D semiconductor packaging market presents significant opportunities, these restrictions highlight the challenges that must be addressed for sustained growth. Overcoming these barriers will require ongoing innovation, investment, and collaboration across the semiconductor industry.

The trend toward smaller, more powerful devices (like smartphones and wearables) necessitates compact packaging solutions. As the Internet of Things expands, there's a growing need for small, efficient, and integrated components. Ongoing improvements in through-silicon vias and wafer-level packaging techniques enhance the feasibility and performance of 3D packaging. The ability to combine different types of chips (logic, memory, analog) in a single package improves functionality and efficiency. The key players operating in the market are focused on developing and introduction 3D packaging semiconductor services, which is estimated to create lucrative opportunities for the growth of the 3D semiconductor packaging market over the forecast period.

Leading chipmakers, including Intel, Samsung, and TSMC, are vying with one other for cutting-edge packaging technology that has the ability to vertically connect many chips or integrate other semiconductors. It is possible to package and integrate several components into a single electronic device due to advanced packaging technology.

The 3D packaging offers manufacturers a packaging solution that is naturally flexible. This ability to make any semiconductor devices match to its exact needs of different applications is an advantage of this type of packaging. The flexibility feature can support packaging solutions that can be customizable or personalized depending on the client needs. It will enable the 3D packaging markers to offer organizations options of targeting specific market with tailor made solutions. 3D packaging provides a versatility which will aid in creating customized solutions that could help capitalize on niche markets and consumer demands for personalization. There is a growing prevalence amongst businesses and consumers for personalized and customized products that suit their specific requirements. This will provide a new avenue for the 3D packaging market in the forecast period.

Among them is Intel 3-T, which is shortly to be manufacturing ready and is optimized with through-silicon vias for 3D advanced packaging designs. Mature process nodes are also highlighted, including the newly anticipated 12 nanometer nodes from the joint work with UMC that was revealed in January 2024. Customers will be able to create and deliver goods that are specifically adapted to their demands due to these evolutions. Intel Foundry promises a new node every two years and node evolutions along the way, allowing clients a roadmap to continuously expand their offerings on Intel's leading process technology. Along with FCBGA 2D, Intel also revealed the inclusion of Intel Foundry FCBGA 2D+ to its extensive range of SAT products.

3D through silicon via segment held a dominant presence in the 3D semiconductor packaging market in 2023. 3D Through-Silicon Via (TSV) technology is widely used in semiconductor packaging for high density and compact design, improved performance, enhanced thermal management and lower power consumption.

TSVs allow for vertical stacking of multiple chips, significantly reducing the overall footprint of the package while maintaining high functionality. 3D Through-Silicon Via (TSV) enables different types of chips (logic, memory, sensors) to be integrated within a single package, TSVs facilitate complex system designs. TSVs shorten the distance between chips, which lowers resistance and inductance, resulting in faster signal transmission and improved overall performance. The ability to have multiple vertical connections increases the bandwidth of data transfer between stacked dies, crucial for high-performance applications.

3D Through-Silicon Via (TSV) technology can be designed to improve thermal conduction between chips, allowing for better heat management in densely packed configurations, which is vital for maintaining performance and reliability. 3D Through-Silicon Via (TSV) technology supports various applications, from consumer electronics to high-performance computing, making it versatile for different market needs.

For instance,

The 3D wire bonded segment is expected to grow at the fastest rate in the 3D semiconductor packaging market during the forecast period of 2024 to 2034. 3D wire bonding technology is an advanced semiconductor packaging technique that enhances the performance and functionality of integrated circuits. The 3D wire bonded technology holds special benefits such as space efficiency, cost-effectiveness, increased functionality, and scalability.

3D wire bonded reduces the footprint of the device, making it ideal for compact electronics. Lower interconnect lengths reduce resistance and improve signal integrity, leading to better overall performance. 3D wire bonded technology potentially lowers costs in materials and assembly due to reduced package size and increased manufacturing efficiency. It allows for multi-chip integration, enabling more complex functionalities in smaller devices. 3D wire bonded technology facilitates scaling for high-volume production, supporting the growing demands of modern electronics.

The organic substrate segment held a significant share of the 3D semiconductor packaging market in 2023. Organic substrate products are increasingly used for 3D packaging in semiconductors due to its flexibility and lightweight. Organic substrates are lighter and more flexible compared to traditional ceramic or metal substrates, making them easier to handle and integrate into compact designs. They are generally less expensive to manufacture, which is crucial for high-volume production. The material costs and processing methods for organic substrates are often more economical.

Organic substrates allow for complex geometries and designs, accommodating various chip sizes and configurations necessary for 3D integration. Organic substrates have shown improved performance in terms of yield rates and reliability over time, which is critical for consumer electronics. Many organic substrates are more environmentally friendly than traditional materials, aligning with industry trends toward sustainable practices. These factors collectively contribute to the widespread adoption of organic substrates in 3D packaging for semiconductors, meeting the demands for performance, efficiency, and cost-effectiveness in modern electronics.

The automotive & transportation segment led the global 3D semiconductor packaging market. Semiconductors are essential for ADAS technologies such as adaptive cruise control, lane-keeping assist, and collision avoidance systems, enhancing vehicle safety and automation. Modern vehicles are equipped with connectivity features like GPS, infotainment systems, and vehicle-to-everything (V2X) communication, all of which rely heavily on semiconductors.

The rise of electric vehicles necessitates sophisticated semiconductor components for battery management systems, power electronics, and electric drive controls, improving efficiency and performance. Modern vehicles are equipped with connectivity features like GPS, infotainment systems, and vehicle-to-everything (V2X) communication, all of which rely heavily on semiconductors. Semiconductors play a crucial role in enabling the processing power needed for sensors, cameras, and LIDAR systems that support autonomous vehicle technology. Advanced semiconductors help improve fuel efficiency and reduce emissions through better engine control and power management systems.

High-quality semiconductor components are essential for critical systems, ensuring reliability and safety in automotive applications. Consumers demand more features, including enhanced safety, entertainment, and comfort options, driving the need for more semiconductor integration. Increasing regulations around emissions and safety standards require more sophisticated electronic control systems, all dependent on semiconductor technology.

The electronics segment is expected to grow at the fastest rate in the 3D semiconductor packaging market during the forecast period of 2024 to 2034. 3D packaging allows for more components to be integrated into a smaller footprint, which is crucial for compact electronic devices. Shorter interconnects in 3D configurations reduce signal loss and latency, improving overall performance and power efficiency. Stacking multiple chips can integrate various functions (e.g., logic, memory) into a single package, simplifying design and enhancing capabilities. 3D packaging facilitates the integration of heterogeneous materials and technologies, such as combining analog, digital, and RF components in a single package. These benefits make 3D packaging an attractive choice in the electronics sector, where performance, miniaturization, and functionality are paramount.

Asia Pacific region dominated the global 3D semiconductor packaging market in 2023. The Asia-Pacific region dominates the 3D semiconductor packaging market, primarily due to the presence of leading semiconductor manufacturers and a booming consumer electronics market. Rapid adoption of 5G technology and the rise of IoT applications drive the need for advanced packaging solutions.

Countries like Taiwan, South Korea, and Japan have well-established semiconductor manufacturing ecosystems, housing major foundries and suppliers. The region benefits from lower labor costs and efficient manufacturing processes, allowing for competitive pricing. Asia-Pacific is home to some of the largest consumer electronics markets in the world, particularly in China, where demand for smartphones, tablets, and other devices drives semiconductor requirements. The swift adoption of new technologies, including 5G, IoT, and AI, fuels the need for advanced packaging solutions.

The countries in Asia Pacific are investing heavily on research and development activities. This has led to innovations in the packaging technologies such as 3D packaging. The region’s strong partnerships between academic research and the semiconductor industry is a crucial factor in advancements of semiconductor technologies. In China and Japan, a noticeable shift towards autonomous as well as electric vehicles have surged the demand of advanced technology semiconductor packaging solutions. This region has a well-established and developed supply chain which has proven to be an aspect that supports the semiconductor manufacturing at various levels from design to packaging to testing.

Companies in the Asia-Pacific region are often quick to adapt to market changes and technological advancements, ensuring they remain competitive in the global landscape. The combination of a robust manufacturing base, high demand for consumer electronics, significant investments in R&D, and supportive government policies positions the Asia-Pacific region as a leader in the 3D semiconductor packaging market. This dominance is likely to continue as technological advancements and market needs evolve. The key players operating in the Asia Pacific region are focused on introduction of the 3D packaging semiconductor which is estimated to drive the growth of the 3D semiconductor packaging market in Asia Pacific region.

For instance,

North America region is anticipated to grow at the fastest rate in the 3D semiconductor packaging market during the forecast period. North America is home to many leading semiconductor companies and technology giants, including Intel, AMD, and NVIDIA, driving innovation and investment in advanced packaging technologies. These companies invest heavily in research and development, fostering advancements in 3D packaging techniques. The growing demand for AI and machine learning applications requires high-performance computing solutions, which benefit from 3D packaging for better performance and efficiency.

Increased need for data centers and supercomputing capabilities drives the adoption of 3D packaging to optimize space and power consumption. A well-developed supply chain in North America supports all aspects of semiconductor design, manufacturing, and packaging, facilitating the growth of advanced packaging solutions. Companies in North America are often quick to adapt to changing market conditions and technological trends, ensuring they remain competitive.

The growth of the 3D semiconductor packaging market in North America is fueled by a combination of technological innovation, strong demand from emerging applications, and the region's robust ecosystem. As industries evolve and new technologies emerge, the market is expected to continue expanding, positioning North America as a key player in the global semiconductor landscape.

In North America, the U.S., plays an important role in boosting the semiconductor packaging industry in the region. U.S. holds a big share of the market in this region and will continue to be a crucial country for the semiconductor industry in the forecast period. U.S. is spending on research and development activities for technological advancements; semiconductor industry is the second highest in the country investing for innovations. There is an increasing demand for semiconductor packaging in the country which is anticipated to surge in the coming years.

![]()

By Technology

By Material

By Industrial Vertical

By Region

April 2025

April 2025

April 2025

April 2025